T Flip Flop Timing Diagram

We will assume an initial condition t 0 of q being low and q being high. Toggle t flip flop.

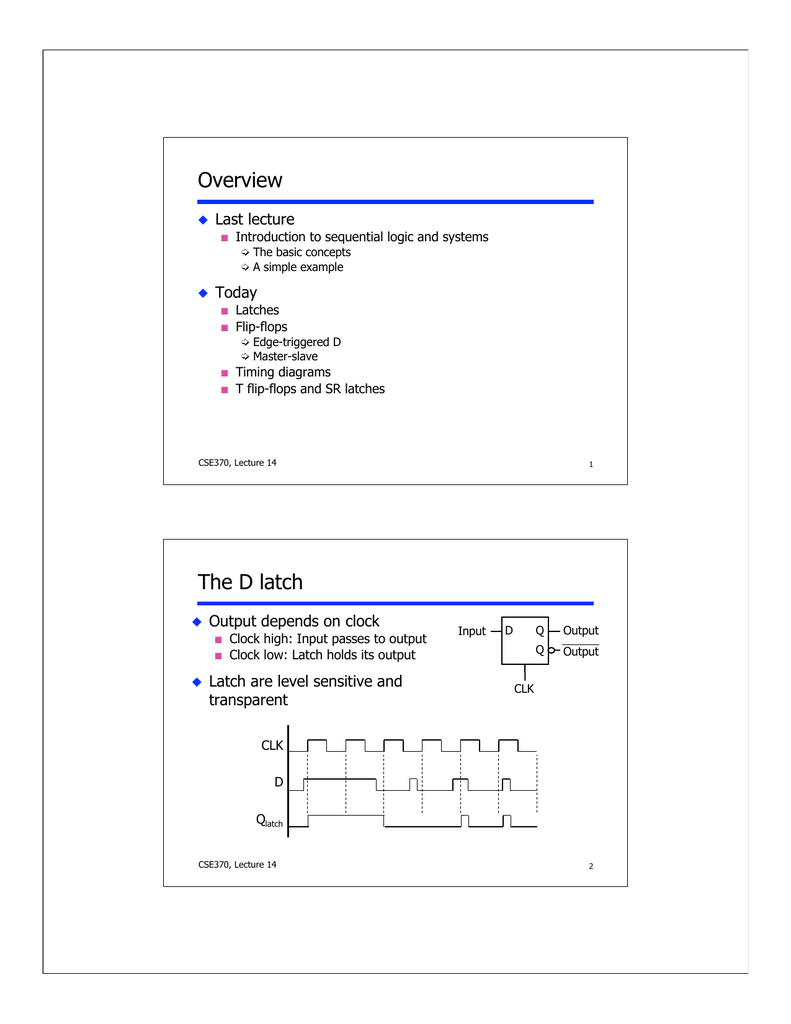

Overview last lecture introduction to sequential logic and systems the basic concepts a simple example today latches flip flops edge triggered d master slave timing diagrams t flip flops and sr latches cse370 lecture 14 2 the d latch output depends on clock clock high.

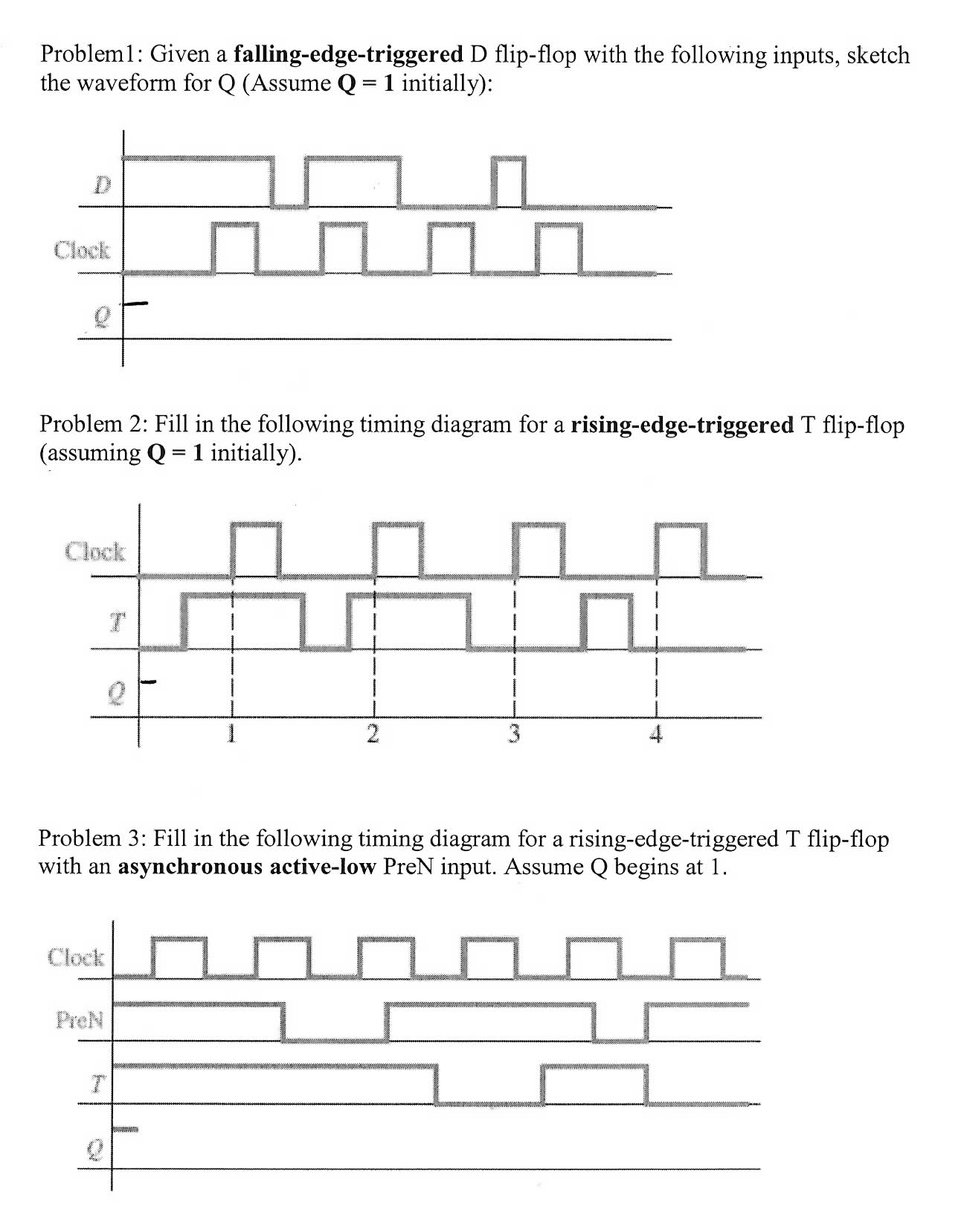

T flip flop timing diagram. Sequential circuit description d c d c clock x a a b b y. The timing diagram in figure 3 15 view b shows the toggle input and the resulting outputs. Edge triggered flip flop state table state diagram.

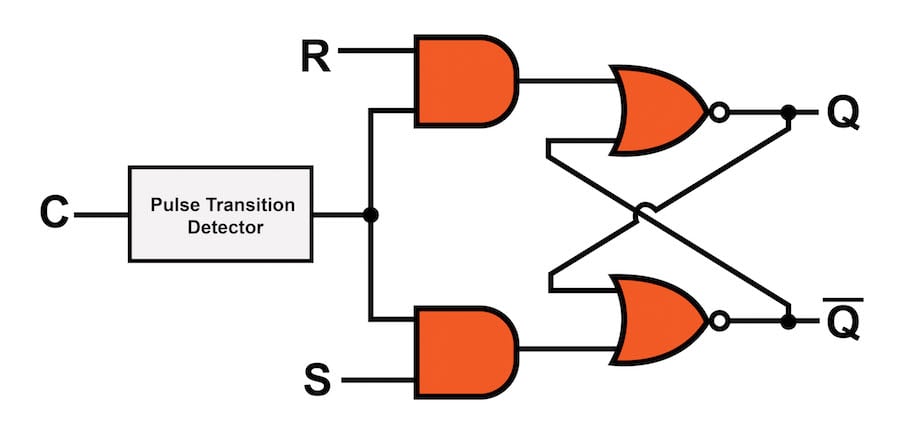

Sequential circuit description input equations state table state diagram well use the following example. In this video i have discussed about the s r flip flop which is known as setreset flip flop. Slide 43 of 50.

I talked about the edge triggered s r flip flop and also discussed its truth table and timing diagram. T s input needs to be stable before trigger hold time. Input passes to output.

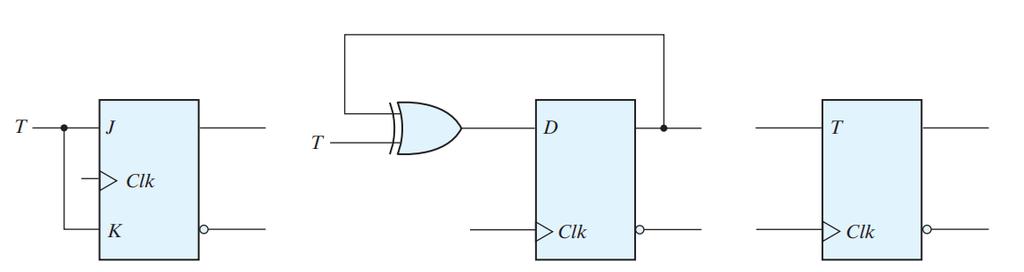

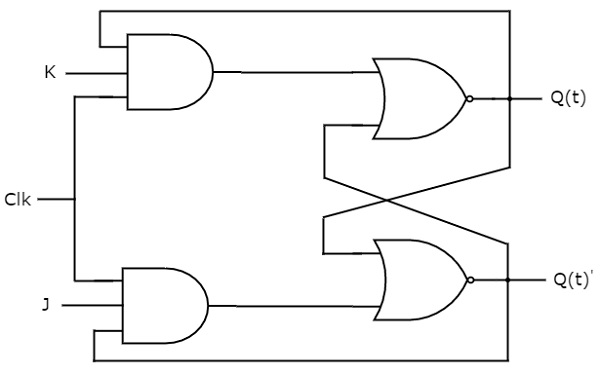

A description of the jk and t flip flops along with some example timing diagrams showing how they work. Flip flop timing set up time. Slide 43 of 50.

T Is For Toggle Understanding The T Flip Flop

T Is For Toggle Understanding The T Flip Flop

Solved Given A Falling Edge Triggered D Flip Flop With Th

Solved Given A Falling Edge Triggered D Flip Flop With Th

Master Slave Jk Flip Flop Timing Diagram Fabulous Jk Flip Flops

Sequential Digital Design Laboratory Manual Experiment 3 Flip

Sequential Digital Design Laboratory Manual Experiment 3 Flip

Frequency Division Using Divide By 2 Toggle Flip Flops

Frequency Division Using Divide By 2 Toggle Flip Flops

Elegant Of D Flip Flop Timing Diagram For An Asynchronous Youtube

Elegant Of D Flip Flop Timing Diagram For An Asynchronous Youtube

Flip Flop Electronics Wikipedia

Flip Flop Electronics Wikipedia

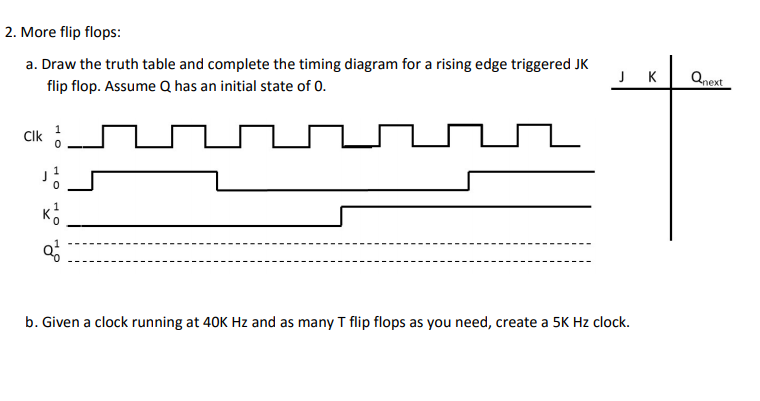

Solved 2 More Flip Flops A Draw The Truth Table And Co

Solved 2 More Flip Flops A Draw The Truth Table And Co

Timing Diagram For T Flip Flop Beautiful Flip Flops Flow Block Diagram

Flip Flops In Electronics T Flip Flop Sr Flip Flop Jk Flip Flop D

Digital Circuits And Systems Circuits I Sistemes Digitals Csd

0 Response to "T Flip Flop Timing Diagram"

Post a Comment